# Advance Information

# Low-Power Dual Tone Multiple Frequency Receiver

The MC145436A is a low-power and improved input sensitivity version of the MC14LC5436.

The MC145436A is a silicon gate CMOS LSI device containing the filter and decoder for detection of a pair of tones conforming to the DTMF standard with outputs in hexadecimal. Switched capacitor filter technology is used together with digital circuitry for the timing control and output circuits. The MC145436A provides excellent power line noise and dial tone rejection and is suitable for applications in central office equipment, PABX, and keyphone systems, remote control equipment and consumer telephony products.

The MC145436A offers the following performance features:

- Single + 5 V Power Supply

- Detects All 16 Standard Digits

- Uses Inexpensive 3.58 MHz Crystal

- · Provides Guard Time Controls to Improve Speech Immunity

- Output in 4-Bit Hexadecimal Code

- . Built-In 60 Hz and Dial Tone Rejection

- . Pin Compatible with SSI-204, MC145436, and MC14LC5436

- Functional and Applicational Compatible with MC145436 and MC14LC5436

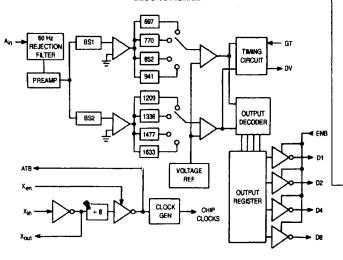

#### **BLOCK DIAGRAM**

# MC145436A

# ORDERING INFORMATION MC145436AP Plastic DIP MC145436ADW SOG Package

####

| SOG                |     |    |                    |  |

|--------------------|-----|----|--------------------|--|

| D2 (               | 1 • | 16 | ) D4               |  |

| D1 (               | 2   | 15 | 3 06               |  |

| ENB (              | 3   | 14 | þον                |  |

| VDD (              | 4   | 13 | 3 NC               |  |

| NC (               | 5   | 12 | BTA (              |  |

| GT [               | 6   | 11 | ) X <sub>in</sub>  |  |

| X <sub>en</sub> (  | 7   | 10 | ) x <sub>out</sub> |  |

| Ain (              | 8   | 9  | ) GND              |  |

| NC = NO CONNECTION |     |    |                    |  |

## MAXIMUM RATINGS (Voltages Referenced to GND Unless Otherwise Noted)

| Rating                            | Symbol | Yalue                                         | Unit |

|-----------------------------------|--------|-----------------------------------------------|------|

| DC Supply Voltage                 | VDD    | - 0.5 to + 6.0                                | ٧    |

| Input Voltage, Any Pin Except Ain | Vin    | - 0.5 to V <sub>DD</sub> + 0.5                | ٧    |

| Input Voltage, Ain                | Vin    | V <sub>DD</sub> - 10 to V <sub>DD</sub> + 0.5 | ٧    |

| DC Current Drain per Pin          | T      | ± 10                                          | mA   |

| Power Dissipation                 | PD     | 100                                           | mW   |

| Operating Temperature Range       | TA     | - 40 to + 85                                  | ပ္   |

| Storage Temperature Range         | Tstg   | - 65 to + 150                                 | ပ္   |

This device contains circuitry to protect the inputs against demage due to high static voltages or electric fields: however, it is advised that normal precautions be taken to avoid applications of any voltage higher than the maximum reted voltages to this high impedence circuit.

For proper operation it is recommended that V<sub>In</sub> and V<sub>Out</sub> be constrained to the range V<sub>SS</sub> <- (V<sub>In</sub> or V<sub>Out</sub>) ≤ V<sub>ID</sub>. Rehability of operation is enhanced if unused inputs are tied to and appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>).

#### **ELECTRICAL CHARACTERISTICS**

(All Polarities Referenced to VSS = 0 V, VDD = 5.0 V ± 10%, TA = -40 to + 85°C, Unless Otherwise Noted)

| Parameter                                    |                                              | Symbol | Min | Тур      | Mex        | Unit |

|----------------------------------------------|----------------------------------------------|--------|-----|----------|------------|------|

| DC Supply Voltage                            |                                              | VDD    | 4.5 | 5        | 5.5        | ٧    |

| Supply Current (fCLK = 3.58 MHz)             |                                              | ipo    | _   | 5        | 8          | mA   |

| Input Current                                | GT<br>ENB, X <sub>in</sub> , X <sub>en</sub> | lin    | =   | =        | 450<br>± 1 | μА   |

| Input Voltage Low                            | ENB, GT, X <sub>en</sub>                     | VIL    |     | -        | 1.5        | V    |

| Input Voltage High                           | ENB, GT, Xen                                 | VIH    | 3.5 | <b>—</b> | _          | ٧    |

| lout Data and DV Pins: Vout = 4.5 V (Source) |                                              | Юн     | 800 |          | <b>-</b> _ | μА   |

| lout Data and DV Pins: Vout = 0.4 V (Sink)   |                                              | lOL    | 1.0 | _        |            | mA   |

| Input Impedance                              | Ain                                          | Rin    | 90  | 100      | T -        | kΩ   |

| Fanout                                       | ATB                                          | Fout   |     | _        | 10         |      |

| Input Capacitance                            | X <sub>en</sub> . ENB                        | Cin    | -   | 6        | -          | pF   |

#### ANALOG CHARACTERISTICS (Vpp = 5.0 V ± 10%, Ta = -40 to + 85°C, Unless Otherwise Noted)

| Parameter                                             | Min            | Тур   | Mex   | Unit   |

|-------------------------------------------------------|----------------|-------|-------|--------|

| Signal Level for Detection (Ain)                      | -35            |       | - 2   | dBm    |

| Twist = High Tone/Low Tone                            | -10            |       | 10    | dB     |

| Frequency Detect Bandwidth                            | ± (1.5 + 2 Hz) | ± 2.5 | ± 3.5 | %60    |

| 60 Hz Tolerance                                       | -   -          |       | 0.8   | Vrms   |

| Dial Tone Tolerance (Note 1)<br>(Dial Tone 330 + 440) | -              | -     | 0     | dB     |

| Noise Tolerance (Notes 1 and 2)                       | -              |       | - 12  | dB     |

| Power Supply Noise (Wide Band)                        |                |       | 10    | mV p⊸p |

| Talk Off (Mitel Tape #CM7290)                         |                | 2     | T -   | Hits   |

### NOTES:

- 1. Pleferenced to lower amplitude tone.

- 2. Bandwidth limited (0 to 3.4 kHz) Gaussian Noise.

## PIN DESCRIPTIONS

#### Vnn

Positive Power Supply (PDIP, SOG - Pin 4)

The digital supply pin, which is connected to the positive side of the power supply.

#### Vss

Ground (PDIP - Pin 8, SOG - Pin 9)

Ground return pin is typically connected to the system ground.

#### D1, D2, D4, D8

Data Output (PDIP — Pins 2, 1, 14, 13; SOG — Pins 2, 1, 16, 15)

These digital outputs provide the hexadecimal codes corresponding to the detected digit. The digital outputs become valid after a tone pair has been detected and are cleared when a valid pause is timed. See Table 1 for hexadecimal codes. These output pins are high impedance when the enable pin is at looic 0.

# ENB

Enable (PDIP, SOG — Pin 3)

Outputs D1, D2, D4, D6 are enabled when ENB is at a logic 1, and high impedance (disabled) when ENB is at a logic 0.

## GT

## Guard Time (PDIP -- Pin 5, SOG -- Pin 6)

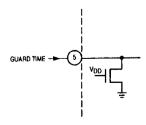

The guard time control input provides two sets of detected time and release time, both within the allowed ranges of tone on and tone off (see Figure 1). A longer tone detect time rejects signals too short to be considered valid. With GT=1, talk off performance is improved, since it reduces the probability that tones simulated by speech will maintain signal conditions long enough to be accepted. In addition, a shorter release time reduces the probability that a pause simulated by an interrupt in speech will be detected as a valid pause. On the other hand, a shorter tone detect time with a long

**Table 1. Hexadecimal Codes**

|       | Output Code |    |    |           |  |

|-------|-------------|----|----|-----------|--|

| Digit | D6          | 04 | D2 | <b>D1</b> |  |

| 1     | 0           | 0  | 0  | 1         |  |

| 2     | 0           | 0  | 1  | 0         |  |

| 3     | 0           | 0  | 1  | 1         |  |

| 4     | 0           | 1  | 0  | 0         |  |

| 5     | 0           | 1  | 0  | 1         |  |

| 6     | 0           | 1  | 1  | 0         |  |

| 7     | 0           | 1  | 1  | 1         |  |

| 8     | 1           | 0  | 0  | 0         |  |

| 9     | 1           | 0  | 0  | 1         |  |

| 0     | 1           | 0  | 1  | 0         |  |

| •     | 1           | 0  | 1  | 1         |  |

| *     | 1           | 1  | 0  | 0         |  |

| Α     | 1           | 1  | 0  | 1         |  |

| В     | 1           | 1  | 1  | 0         |  |

| С     | 1           | 1  | 1  | 1         |  |

| D     | 0           | 0  | 0  | 0         |  |

release time would be appropriate for an extremely noisy environment where fast acquisition time and immunity to dropouts would be required. In general, the tone signal time generated by a telephone is 100 ms, nominal, followed by a pause of about 100 ms. A high-to-low or low-to-high transition on the GT pin resets the internal logic and the MC145438A is immediately ready to accept a new tone input. If left open, this pin is internally pulled to ground.

#### Xen Oscillator Enable (PDIP --- Pin 6, SOG --- Pin 7)

A logic 1 on  $X_{en}$  enables the on-chip crystal oscillator. When using alternate time base from the ATB pin,  $X_{en}$  should be tied to  $V_{SS}$ .

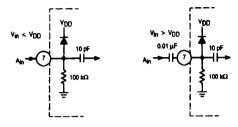

# Anelog Input (PDIP — Pin 7, SOG — Pin 8)

This pin accepts the analog input and is internally blased so that the input signal may be ac coupled. The input may be do coupled so long as it does not exceed the positive supply (see Figure 2).

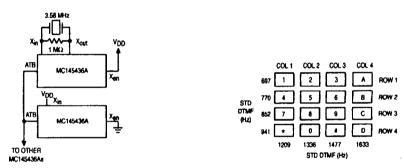

#### Xin/Xout Oscillator in and Oscillator Out (PDIP — Pins 10, 9; SOG — Pins 11, 10)

These pins connect to an internal crystal oscillator. In operation, a parallel resonant crystal is connected from  $X_{in}$  to  $X_{out}$ , as well as a 1 M $\Omega$  resistor in parallel with the crystal. When using the alternate clock source from ATB,  $X_{in}$  should be tied to  $Y_{DD}$ .

#### ATB

#### Alternate Time Base (PDiP - Pin 11, SOG - Pin 12)

This pin serves as a frequency reference when more than one MC145436A is used, so that only one crystal is required for multiple MC145436As. When doing so, all ATB pins should be tied together as shown in Figure 3. When only one MC145436A is used, this pin should be left unconnected. The output frequency of ATB is 447.4 kHz.

#### DV Data Valid (PDIP — Pin 12, SOG — Pin 14)

DV signals a detection by going high after a valid tone pair is sensed and decoded at output pins D1, D2, D4, D8. DV remains high until a loss of the current DTMF signal occurs or until a transition in GT occurs.

Figure 1. Guard Time

MOTOROLA

Figure 2. Analog Input (Operational Information Based on PDIP Package)

Figure 3. Multiple MC145436As

Figure 4. 4 × 4 Keyboard Matrix